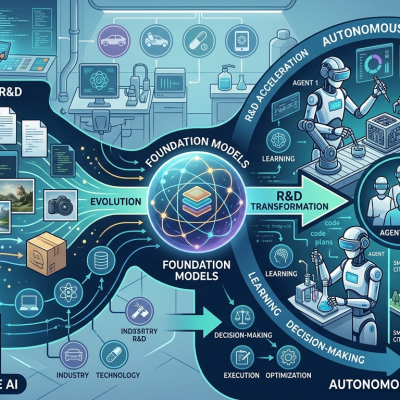

AI is no longer a buzzword—it’s the backbone of modern innovation. From recommendation engines to autonomous systems, AI is everywhere. But while much of the spotlight has been on inference—the act of running trained models—the true battlefield for silicon architects and hyperscalers lies in training.

Training is where models are born, and it’s also where the bleeding edge of compute architecture is being forged. Despite the operational costs and latency concerns of inference at scale, it is the massive compute demands of training large models that are reshaping the semiconductor industry.

Why Training Is the Real Driver

Training today’s most advanced models—like GPT-4, Gemini, and Claude—requires compute cycles that dwarf those needed for inference. We’re talking about models with hundreds of billions of parameters trained on petabytes of data. GPT-4, for instance, is estimated to have used tens of thousands of GPUs over weeks or months to complete training runs.

This scale of computation has made training the dominant workload influencing hardware design. While inference gets the headlines, training gets the silicon.

Architectural Shifts in Response

To meet these needs, chipmakers are moving beyond general-purpose GPUs to purpose-built accelerators. NVIDIA’s Hopper architecture, Google’s TPU v4, and AMD’s MI300 are all optimized for dense matrix operations, high memory bandwidth, and interconnect efficiency—all critical for training.

Take NVIDIA’s H100 GPU with its Transformer Engine. It’s not just about FP16 or FP32 throughput anymore. The H100 can dynamically use FP8 for even more efficient training, accelerating large language model (LLM) performance by up to 9x compared to its predecessor, according to recent industry benchmarks.

And it doesn’t stop there. The semiconductor process node race—from 7nm down to 3nm and soon 2nm—is being driven largely by the need to cram more transistors for parallelism and power efficiency, both of which are essential for training workloads.

The Economics of Training

Training a frontier model can cost tens to hundreds of millions of dollars. That cost is front-loaded—once trained, the model can be run many times for inference. But that initial barrier means only a few players can afford to compete: OpenAI, Google DeepMind, Anthropic, Meta, and a handful of others.

This is creating a bifurcation in the AI economy: those with the compute to train massive models, and those who must license or build on top of them.

Key Insights

- Training compute demand is growing exponentially faster than inference, driving specialized hardware innovation.

- Advanced process nodes (5nm, 3nm, etc.) are being prioritized for AI accelerators, not traditional CPUs.

- Power efficiency is now measured in training throughput per watt, not just inference latency.

- Vertical integration (e.g., Google designing its own TPUs) is becoming critical to manage training costs and latency.

- Economic moats are forming around those who can afford to train frontier models, shifting competitive dynamics in tech.

So What?

The implications are enormous. Cloud providers are racing to offer optimized training infrastructure. Semiconductor companies are realigning roadmaps. And major tech players are consolidating power through proprietary foundation models. In this new AI economy, compute is currency—and training is the mint.

What’s Next?

As the gap between training and inference grows, how will smaller players compete in an AI landscape increasingly dominated by those who control the training stack?

#AITraining #Semiconductors #LLMs #NVIDIAH100 #TPUs #AIInfrastructure #TechStrategy